Very low power wireless transceiver integrated chip CC1000

Abstract: Introduce the circuit structure and typical application design of a wireless transceiver IC CC1000; highlight the timing required for communication between CC1000 and a microcontroller.

introduction

CC1000 is an ideal UHF monolithic transceiver chip manufactured under Chipcon's SmartRF technology in a 0.35μm CMOS process. Its working frequency band is 315, 868 and 915MHz, but CC1000 can be easily programmed to work in the range of 300 ~ 1000MHz. It has low voltage (2.3 ~ 3.6V), extremely low power consumption, programmable output power (-20 ~ 10dBm), high sensitivity (generally -109dBm), small size (TSSOP-28 package), integrated bit synchronizer Features. Its FSK data transmission can reach 72.8Kbps, with 250Hz steps programmable frequency capability, suitable for frequency hopping protocol; the main working parameters can be changed through the serial bus interface programming, very flexible to use.

Figure 1 Simplified block diagram of CC1000

1 Circuit structure

Figure 1 shows a simplified block diagram of CC1000. In receiving mode, CC1000 can be regarded as a traditional superheterodyne receiver. The radio frequency (RF) input signal is amplified by a low-noise amplifier (LNA) and then flipped into the mixer, and mixed by the mixer to generate an intermediate frequency (IF) signal. In the intermediate frequency processing stage, the signal is amplified and filtered before being sent to the demodulator. The optional RSSI signal and IF signal can also be generated at the pin RSSI / IF by mixing. After demodulation, CC1000 outputs the demodulated digital signal from pin DIO. The synchronization of the demodulated signal is completed by the clock signal provided by PCLK on the chip.

In the transmission mode, the signal output from the voltage controlled oscillator (VCO) is sent directly to the power amplifier (PA). The radio frequency output is controlled by the data added to the DIO pin, called frequency shift keying (FSK). This internal T / R switching circuit makes antenna connection and matching design easier.

The local oscillator signal generated by the frequency synthesizer is sent to the power amplifier in the receiving state. The frequency synthesizer is composed of a crystal oscillator (XOSC), a phase discriminator (PD), a charging pulse, a VCO, and a frequency divider (/ R and / N). The external crystal must be connected to the XOSC pin. Only the external inductor needs to be connected to the VCO Connected.

Figure 2 CC1000 typical application circuit diagram

2 Application circuit

When CC1000 works, there are few peripheral components. The typical application circuit is shown in Figure 2. When configuring different transmission frequencies of CC1000, the parameters of peripheral components are also different. For specific parameters, please refer to Reference [1].

3 Three-wire serial data port

The CC1000 can be programmed via a simple three-wire serial interface (PDATA, PCLK, and PALE). There are 36 8-bit configuration registers, each addressed by a 7-bit address. A complete CC1000 configuration requires 29 data frames to be sent, each 16 bits (7 address bits, 1 read / write bit and 8 data bits). The PCLK frequency determines the time required for full configuration. Working at a PCLK frequency of 10MHz, the time required to complete the entire configuration is less than 60μs. In the low potential mode setting, only one frame needs to be transmitted, and the time required is less than 2 μs. All registers are readable. In each write cycle, the 16-bit byte is sent to the PDATA channel. The 7 most important bits (A6: 0) in each data frame are the address bits, and A6 is the MSB (highest bit), which is sent first. The next transmitted bit is the read / write bit (high-level write, low-level read). During the transmission of the address and the read / write bit, PALE (program address latch enable) must be kept low, and then transfer 8 A data bit (D7: 0), as shown in Figure 3. Table 1 is a description of each parameter. PDATA is valid on the falling edge of PCLK. When the last byte bit D0 in the 8-bit data bit is loaded, the entire data word is loaded into the internal configuration register. The configuration information programmed in the low-potential state is valid, but the power cannot be turned off.

Table 1 Serial interface timing description

| parameter name | Symbol / Unit | Minimum value | Explanation |

| PCLK frequency | fCLOCK / MHz | - | - |

| PCLK low duration | tCL, min / ns | 50 | The minimum time that PCLK stays low |

| PCLK high duration | tCH, min / ns | 50 | The minimum time that PCLK stays high |

| PALE start time | tSA / ns | 10 | The shortest time PALE stays low before PCLK turns to the falling edge |

| PALE duration | tHA / ns | 10 | The shortest time PALE stays low after PCLK turns to the rising edge |

| PDATA start time | tSD / ns | 10 | The shortest time for data on PALE to be ready before PCLK goes to the falling edge |

| PDATA duration | tHD / ns | 10 | After PCLK turns to the falling edge, the shortest time for the data on PALE to be ready |

| Rise Time | trise / ns | - | Maximum value of PCLK and PALE rise time |

| Fall time | tfall / ns | - | Maximum value of PCLK and PALE fall time |

The microcontroller can also read the configuration register through the same interface. First, send 7 address bits, and then set the read / write bit to low level, which is used to initialize the read data. Next, CC1000 returns data from the addressing register. At this time, PDATA is used as an output port. During reading back data (D7: 0), the microcontroller must set it to tri-state, or set to high level when the pin is open. The timing of the read operation is shown in Figure 4.

Figure 3 CC1000 write operation programming timing diagram Figure 4 CC1000 read operation programming timing diagram

4 Connect with microcontroller

The microcontroller uses three output pins for the interface (PDATA, PCLK, PALE). The pin connected to PDATA must be a bidirectional pin for sending and receiving data. The DCLK that provides data timing should be connected to the input of the microcontroller, and the remaining pins are used to monitor the LOCK signal (at pin CHP_OUT). When the PLL is locked, this signal is at a logic high level. Figure 5 is a schematic diagram of the interface between P87LPC762 MCU and CC1000.

The procedure of P87LPC762 microcontroller writing CC1000 internal register is as follows:

write_com (uchar addr, uchar com_data) // Write internal register subroutine

{char i;

addr << = 1;

pale = 0; // Allow address latch

for (i = 0; i <7; i ++) {// send address

addr << = 1;

p_data = CY;

pclk = 0; // rising edge

pclk = 1;

}

p_data = 1; // write operation

pclk = 0;

pclk = 1;

pale = 1; // Prohibit address latch

for (i = 0; i <8; i ++) {

com_data << = 1;

p_data = CY;

pclk = 0;

pclk = 1;

}

}

Conclusion

When modulating data, CC1000 can be set to three different data forms, namely synchronous NRZ mode, synchronous Manchester code mode, asynchronous transmission (UART) mode. In order to meet the strict power loss requirements under battery power supply, CC1000 provides a very convenient power management method. The low level mode is controlled by the MAIN register, and there are separate bits to control the receiving part, transmitting part, frequency synthesis, and crystal oscillator. This independent control can be used to optimize the lowest possible current loss in an application. CC1000's excellent performance makes it mainly used in ISM (industrial, scientific and medical) and SRD (short-range communication).

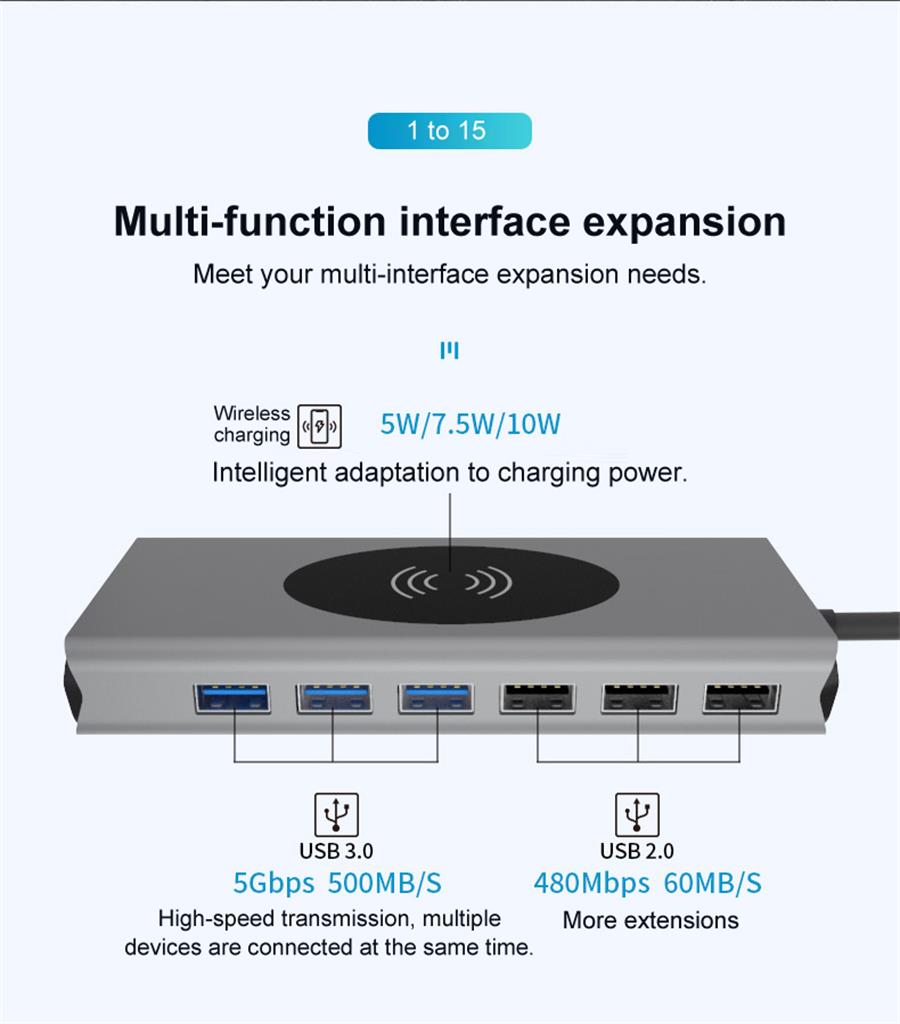

Information technology has penetrated into all areas of our lives. With the progress of technology, the iteration rate of laptops is getting faster and faster. Previous laptops mainly used E-SATA, FireWire, VGA, DisplayPort, SD card slot, USB A, 3.5mm headphone jack, HDMI or RJ45 ports.But manufacturers began stripping connectors from laptops to make them thinner and lighter. Most new laptops now have a USBC port (Thunderbolt or full-featured USBC) and an audio jack. The laptop is thin, but the missing ports are useless. This is where the USB C Hubs comes in.

Type C Usb Hub can support USB, PD, DisplayPort, Thunderbolt, and other protocols. Using USB HUBS, you can extend multiple common connectors directly to your laptop. Mosses are compact, so you can take them anywhere. All peripheral devices are centrally connected to the hub, which reduces the hassle of plugging in and out of the laptop port and makes your desktop cleaner. Let's take a closer look at its capabilities so you can determine how many ports you need.

So these are all important ports on the hub, with the exception of the 3.5mm audio jack. Also, while aesthetics are not important, choosing a nice hub will make you happier. There are rectangular, square, and circular centers on the market to meet your desk setup needs. Usually, the rectangular type is best for your desk because the cables can be well organized if all the ports are on one side of the center.

Usb C Hubs,4 Port Usb C Hub,Usb C Multiport Hub,Usb Hub With Hdmi Port

Henan Yijiao Trading Co., Ltd , https://www.yjusbcable.com