AI and chip design merge, show your talents

Industry vendors and researchers have recently made significant advances in applying machine learning to tricky chip design issues. From a panel discussion at this year's DesignCon conference, the use of artificial intelligence (AI) in electronic design automation (EDA) is currently a hot topic, not only in this conference, but also in several related papers. The discussion also attracted many participants, and the site was packed.

Over the past year, the Machine Learning Center for Advanced Electronics Research (CAEML) has added four new partners. This research team, consisting of 13 industry members and 3 universities, is continuing to expand the breadth and depth of its work.

Christopher Cheng, a distinguished technical expert and CAEML member of Hewlett-Packard Enterprise (HPE), said: "Last year, we focused on signal integrity and power integrity, and this year we divided our product portfolio into system analysis and chips. The layout and trusted platform design have made the greatest progress in the diversity of research."

Paul Franzon, Distinguished Professor at NC State University, said: "Bayesian optimization and convolutional neural networks (CNN) have also significantly improved functionality in design for manufacturability (DFM). Start thinking about using synchronous learning in the design process.†North Carolina State University is one of CAEML's three partner universities.

Madhavan Swaminathan, a professor at Georgia InsTItute of Technology, a school that works with CAMEL, said: "One of the challenges we face is getting the company's data. Because most of their data is proprietary, So we have proposed several processing mechanisms. These processes are currently working well, but still much longer than we expected."

CAEML was founded with ADI, Cadence, Cisco, IBM, Nvidia, Qualcomm, Samsung, and Xilinx. Support from nine vendors such as Xilinx) began with areas of interest including high-speed interconnects, power transmission, system-level electrostatic discharge, IP core reuse, and design rule checking.

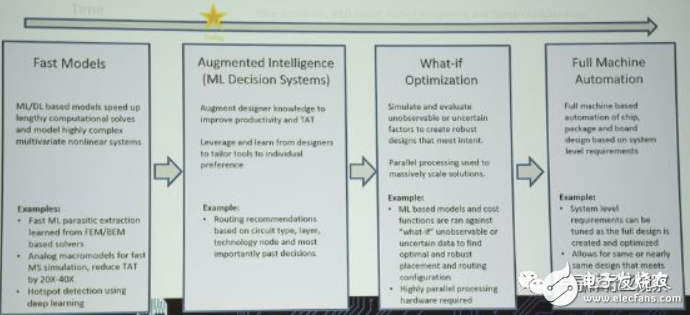

From the development blueprint portrayed by Cadence, the EDA industry is currently entering the second phase of AI applications (Source: Cadence)

EDA vendors such as Cadence Design Systems began researching machine learning as early as the early 1990s. David White, senior director of research and development at Cadence, said the technology was first introduced into its products in 2013, using a version of Virtuoso, and using analysis and data exploration to create machine learning models for parasitic parameters.

To date, Cadence has provided more than 1.1 million machine learning models for its tools to accelerate long-term calculations. The next phase of product development is the layout and routing tools that enable it to learn from human designers and recommend an optimization solution that accelerates uptime. White explained that these solutions may combine local and cloud-based processing to take advantage of parallel systems and large data sets.

Latest developments in machine learning technology and applicationsSynopsys R&D Director Sashi Obilisetty said that at the advanced process nodes, the global rouTIng tool using existing algorithms has reached its limit, so they began to reduce the chip data rate to achieve timing closure.

She added that TSMC used machine learning to predict global winding last year, increasing speed by 40MHz; Nvidia uses machine learning to provide full coverage of chip design while reducing simulation.

Experts who participated in the panel discussion said they saw many opportunities in the industry to automate specific decisions and optimize the overall design process using a variety of machine learning techniques.

Specifically, researchers are exploring opportunities to replace today's simulators with faster AI models. Georgia Institute of Technology's Swaminathan said that relatively slow simulators can cause timing errors, analog circuit imbalances, and insufficient modeling of chip respins. In addition, machine learning can replace IBIS for behavioral modeling in high-speed interconnects.

In addition to the neural network model promoted by Amazon, Google, and Facebook image search and speech recognition services, chip researchers also use data mining, statistical learning, and other tools.

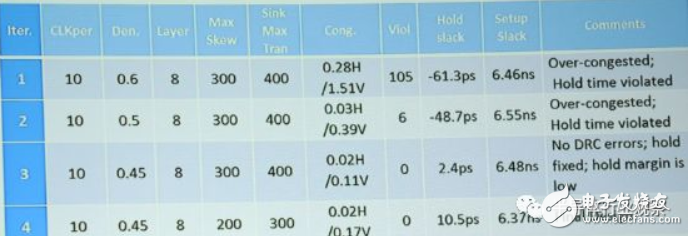

Franzon of North Carolina State University reported using a proxy model to optimize the final entity design in four iterations. In contrast, engineers must perform 20 times. A similar technique is used to calibrate the analog circuit and set up the transceiver for the multi-channel interconnect.

The researchers demonstrated the performance of the agent model in 4 iterations and is expected to replace human designers (20 times)

AI can set dozens of options in EDA tools (sometimes referred to as knobs) to help speed up the automation process. Franzon said: "These tools set up some knobs that are sometimes unclear, and often have a ambiguous relationship with the expected results."

HPE currently uses a combination of neural networks and hyperplane classifiers to predict fault conditions on-site based on solid-state hard disk (SSD) voltage, temperature, and current.

Cheng said: "The amount of data required for training is huge. So far, the classifiers are static, but we want to increase the time dimension of using recurrent neural networks (RNN) instead of just using good/bad tags, then we There will be a TIme-to-failure label. In the future, we also want to extend this work to more parameters and general system failures."

Rf Coaxial Cable,Digital Coaxial Cable,Coaxial Cable For Internet,Coaxial Cable Types

Zhejiang Wanma Tianyi Communication Wire & Cable Co., Ltd. , https://www.zjwmty.com